TMS32C64X DSP引起cache miss 的三种情况以及Cache Coherence一致性的解决办法第一种是:ConfictMisses第二

TMS32C64X DSP引起cache miss 的三种情况以及Cache Coherence一致性的解决办法

第一种是:Confict Misses 第二种是:Capacity Misses 第三种是Complusory

1,2种可以避免,第三种不可避免

Conflict and Capacity Misses

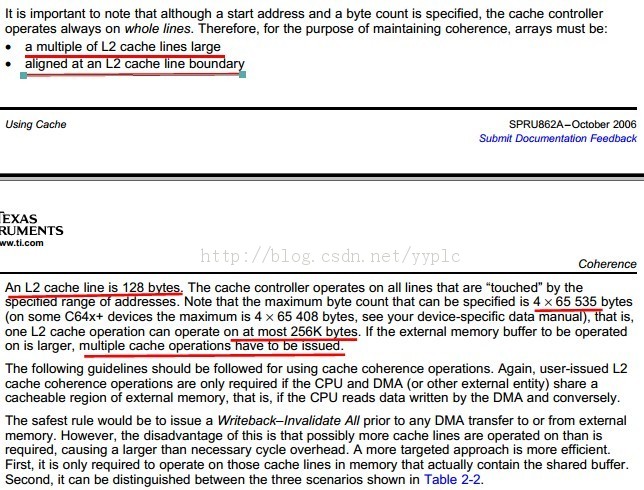

Evictions are caused by conflicts, that is, a memory location is accessed that maps to the same set as a

memory location that was cached earlier. This type of miss is referred to as a conflict miss, a miss that

occurred because the line was evicted due to a conflict before it was reused. It is further distinguished

whether the conflict occurred because the capacity of the cache was exhausted or not. If the capacity was

exhausted, all line frames in the cache were allocated when the miss occurred, then the miss is referred to

as a capacity miss. Capacity misses occur if a data set that exceeds the cache capacity is reused. When

the capacity is exhausted, new lines accessed start replacing lines from the beginning of the array.

Identifying the cause of a miss may help to choose the appropriate measure for avoiding the miss. Conflict

misses mean that the data accessed fits into cache but lines get evicted due to conflicts. In this case, we

may want to change the memory layout so that the data accessed is located at addresses in memory that

do not conflict (map to the same set) in cache. Alternatively, from a hardware design, we can create sets

that can hold two or more lines. Thus, two lines from memory that map to the same set can both be kept

in cache without evicting one another. This is the idea of set-associative caches, described in

Compulsory Misses

In case of capacity misses, one may want to reduce the amount of data that is operated on at a time.

Alternatively, from a hardware design, the capacity of the cache can be increased.

A third category of misses are compulsory misses or first reference misses. They occur when the data is

brought in cache for the first time. Unlike the other two misses, they cannot be avoided, hence, they are

compulsory.

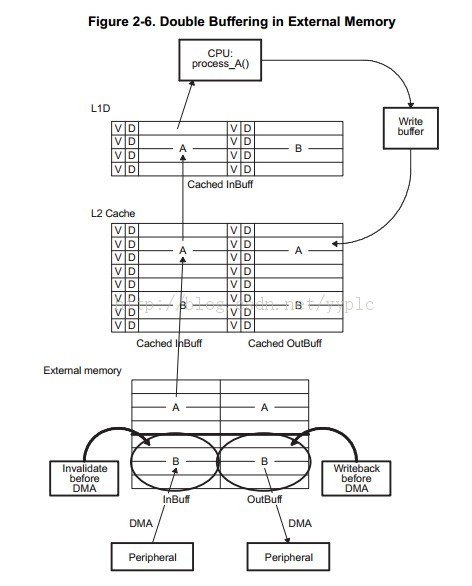

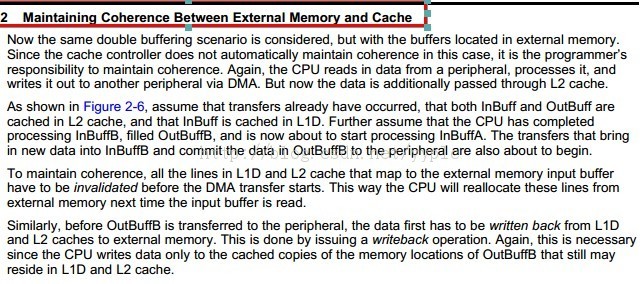

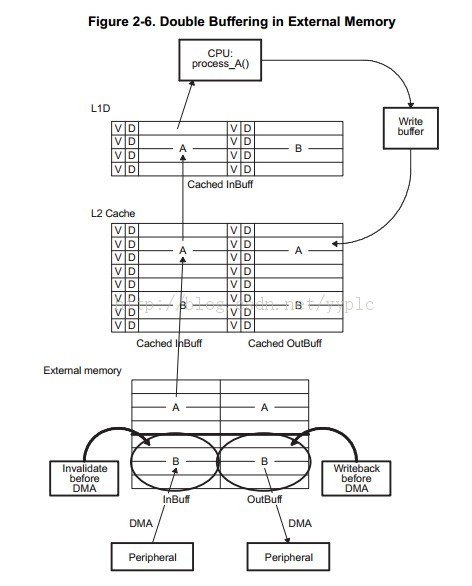

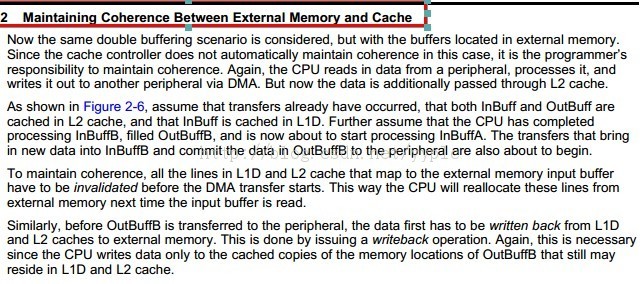

通常情况下,我们在做图像算法法集成的时候,我们在使用DMA的时候,需要解决Cache Coherence问题!

不然会导致DMA copy 数据出现错误的。Cache Coherence 原理描述:

、

、

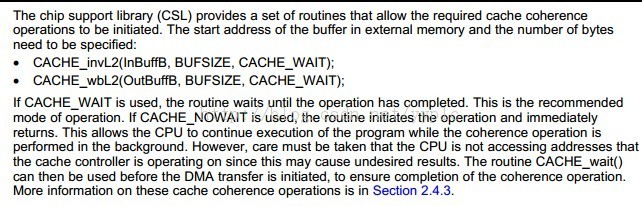

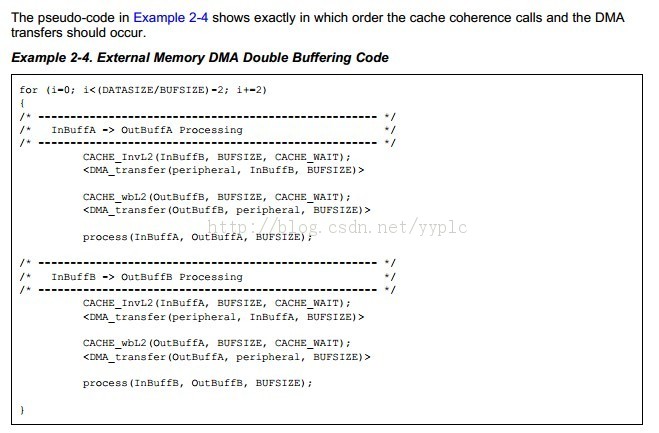

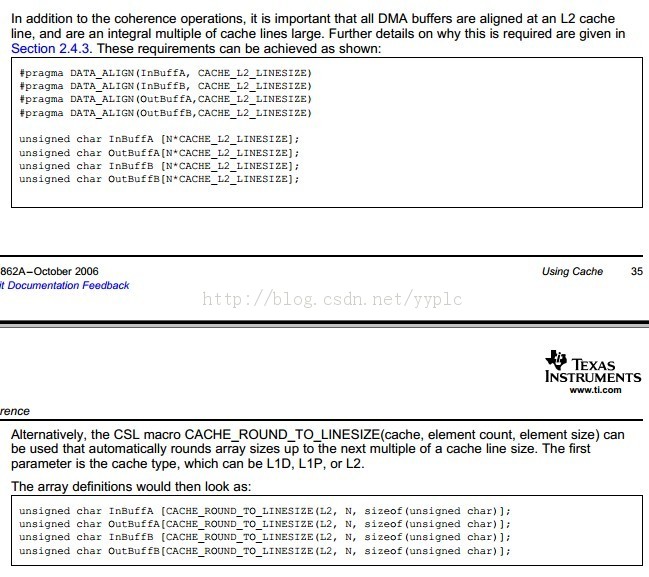

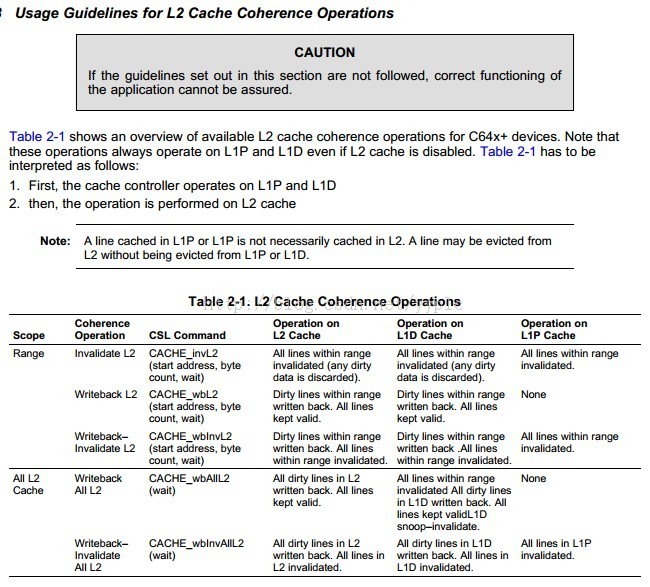

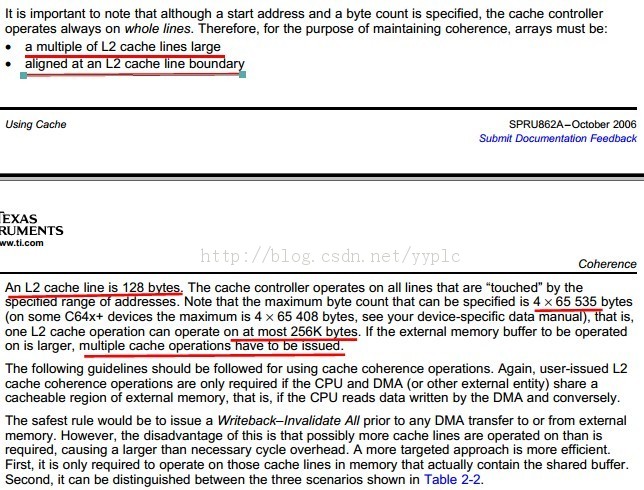

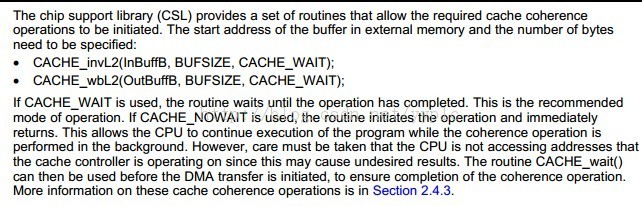

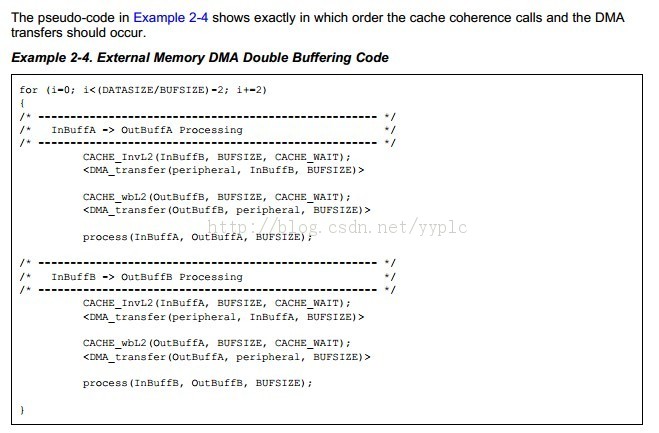

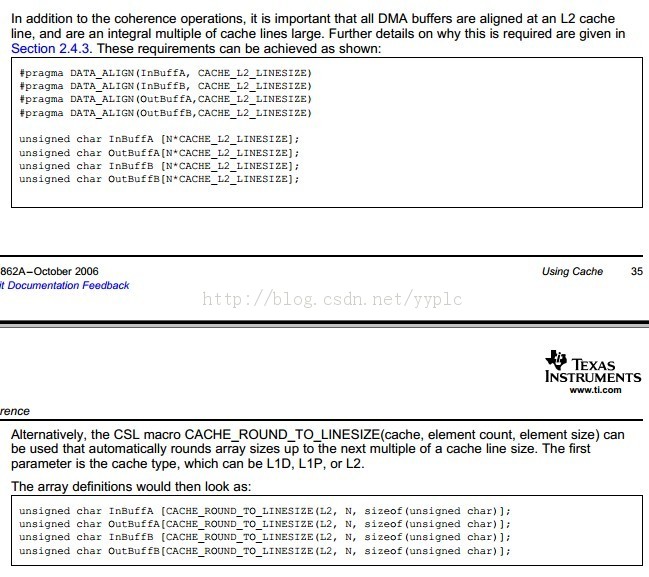

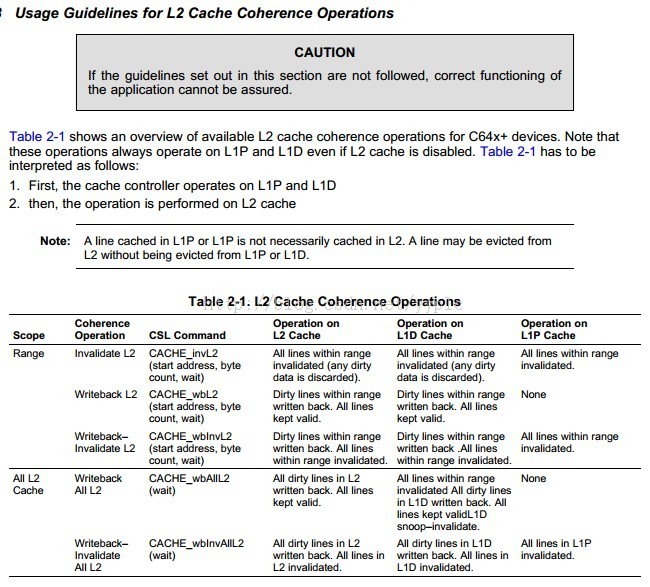

Cache Coherence的解决办法:

文档来自TI spru862.pdf

、

、