了解CPU缓存

Cache 的发展过程

随着CPU制程的提高(486是1微米(μm)制程,现在Intel的主流CPU是0.022微米的制造工艺)

现在 CPU 集成了更多的 Cache, 我们回顾一下:

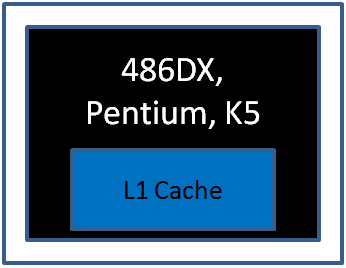

486时代只有 L1 Cache

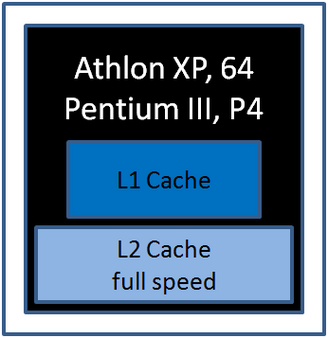

PIII 时代增加了L2 Cache

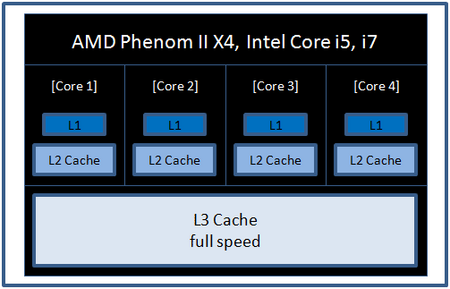

双核时代刚开始时,每个Core都有独立的L1, L2 Cache

现在增加了 L3 Cache

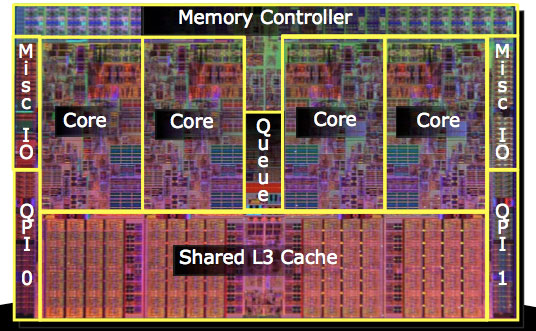

从CPU的未封装表面,可以看到各部分的分布

根据资料说:

在一颗拥有二级 缓存的CPU中,读取一级缓存的命中率为80%。也就是说CPU一级缓存中找到的有用数据占数据总量的80%,剩下的20%从二级缓存中读取。由于不能准 确预测将要执行的数据,读取二级缓存的命中率也在80%左右(从二级缓存读到有用的数据占总数据的16%)。那么还有的数据就不得不从内存调用,但这已经 是一个相当小的比例了。

有三级缓存是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约 5%的数据需要从内存中调用,这进一步提高了CPU的效率。

一级指令缓存,一级数据缓存和二级缓存的区别一级缓存(Level 1 Cache)简称L1 Cache,位于CPU内核的旁边,是与CPU结合最为紧密的CPU缓存,也是历史上最早出现的CPU缓存。由于一级缓存的技术难度和制造成本最高,提高容量所带来的技术难度增加和成本增加非常大,所带来的性能提升却不明显,性价比很低,而且现有的一级缓存的命中率已经很高,所以一级缓存是所有缓存中容量最小的,比二级缓存要小得多。

一般来说,一级缓存可以分为一级数据缓存(Data Cache,D-Cache)和一级指令缓存(Instruction Cache,I-Cache)。二者分别用来存放数据以及对执行这些数据的指令进行即时解码,而且两者可以同时被CPU访问,减少了争用Cache所造成的冲突,提高了处理器效能。目前大多数CPU的一级数据缓存和一级指令缓存具有相同的容量。

二级缓存是CPU性能表现的关键之一,在CPU核心不变化的情况下,增加二级缓存容量能使性能大幅度提高。而同一核心的CPU高低端之分往往也是在二级缓存上有差异,由此可见二级缓存对于CPU的重要性。

动态RAM 电容器就像一个储存电子的小桶。在存储单元中写入1,小桶内就充满电子;写入0,小桶就被清空。这只“桶”的问题在于:它会泄漏。只需大约几毫秒的时间,一个充满电子的小桶就会漏得一干二净。因此,为了确保动态存储器能正常工作,必须由CPU或是由内存控制器对所有电容不断地进行充电,使它们在电子流失殆尽之前保持“1”值。为此,内存控制器会先行读取存储器中的数据,再把数据写回去。这种刷新操作每秒钟会自动进行数千次。动态RAM正是得名于这种刷新操作。它需要不间断地进行刷新,否则就会丢失所保存的数据。这一刷新动作的缺点就是费时,并且会降低内存速度。

静态RAM使用了截然相反的技术。静态RAM用某种形式的触发器来保存内存的每个位.内存单元的触发器由4个或6个晶体管以及一些线路组成,但从来不需要刷新。这使得静态RAM比动态RAM要快得多。但是,由于它所含的部件较多,静态内存单元在芯片上占用的空间会远远超过动态内存单元,使得每个芯片上的内存较小,所以静态RAM要昂贵得多。以前SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作。但现在 CPU和 memory 并不是同一速度

CPU上的 L1-L3 cache 都是静态 RAM,而存储器(memory)是动态RAM

动态RAM的频率提高:DDR DDR DDR3DDR SDRAM是Double Data Rate SDRAM的缩写, SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据.

与DDR相比,DDR2最主要的改进是在内存模块速度相同的情况下,可以提供相当于DDR内存两倍的带宽。与双倍速运行的数据缓冲相结合,DDR2内存实现了在每个时钟周期处理多达4bit的数据。(注意这个时钟周期是指内存的核心频率)

而DDR3 能传送 8 bit 的的数据

内存规格 颗粒核心频率MHz 颗粒工作频率MHz 等效频率MHz

DDR 266/333/400 133/166/200 266/333/400 DDR2 533/667/800 133/166/200 533/667/800 DDR3 1066/1333/1600 133/166/200 1066/1333/1600可能因为动态内存需要费时的动态刷新,所以这些年来核心频率不能提高,所以就采用多个通道读取方法,来提高等效频率,这就是DDR2,DDR3的对DDR改进。

因为内存连接前端总线(FSB), 所以器等效频率与FSB的频率是相同的。

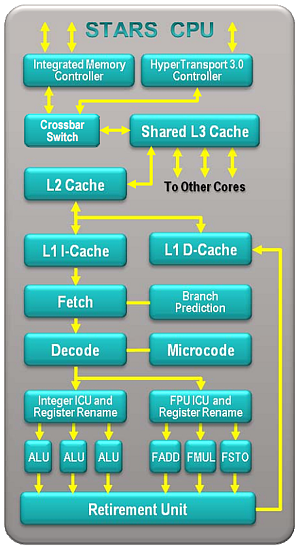

下面是 AMD 第一款4核CPU的 Phenom 9700的数据流,可以看L1,L2 与 core 的其他部件是如何协同的

注:

Microcode: 因为x86 CPU 是 CISC 结构,要把复杂指令转化为微指令

ALU: 一个core 不只一个 ALU单元

Branch Prediction: 可以进行指令预测,从而乱序执行,提高并行度

Register Rename: 寄存器重命名,提高并行度的一种方法

Retirement Unit: 处理Pipe line 的输出结存,并写回

Core 有各系独立的L2 cache, 可能都缓存同一地址的 Memmory, 如何同步呢?

推荐下面的文章 http://blog.csdn.net/zhanglei8893/article/details/6963359

而 L3 cache 是共享的,所以不需要同步

参考:

http://www.tomshardware.com/reviews/athlon-l3-cache,2416-2.html

http://baike.soso.com/v26281515.htm#5

http://www.anandtech.com/show/2960/2

http://www.tomshardware.com/reviews/spider-weaves-web,1728-5.html