深入浅出FPGA-17-xilinx_zynq7000_EPP上一个简单实验(PS+PL)

引言

前面两个实验,PL是传统的FPGA开发,PS是传统的嵌入式开发。

zynq7000EPP是xilinx比较高端的FPGA开发板,XC7Z020内部集成了两个cortexa9的硬核,外部有1G的DDR3,所以单纯做FPGA太浪费了。但是单纯用PS资源,就没必要用FPGA了,所以只有将两者结合使用才能体现其价值所在。

即,PS+PL。添加自己的一个IP到AXI总线上,然后通过SDK编码控制它的寄存器,这就是本小节的实验内容。

17.1 实验目的

1》 熟悉zynq7000 EPP资源和design suite

2》 PL编码,PS编码,实现一个简单逻辑。

17.2 实验环境

Board :ZYNQ7000 EPP

Device:XC7Z020CLG484ACX1221

Design suite:14.1 (PlanAhead+XPS+SDK)

17.3 实验准备

a) 会planAhead创建工程:ps_pl。

b) 简单了解和使用XPS和SDK

17.4 实验内容

a) 添加自己一个IP:rill_ip,挂到AXI上,此IP有一个output连到外部一个LED上。

b) 在SDK编写C代码控制这个IP的寄存器来控制此设备,进而控制LED的闪烁。

17.5 实验步骤

a) 打开planAhead,创建embedded新工程,添加PS7。

b) 打开XPS->hardware,添加自己的ip:rill_ip。

c) AXI4-lite.

d) 一个32位寄存器。

e) 生成driver。

f) 修改此IP的文件:MPD文件,rill_ip.vhd,user_logic.vhd。三个文件。

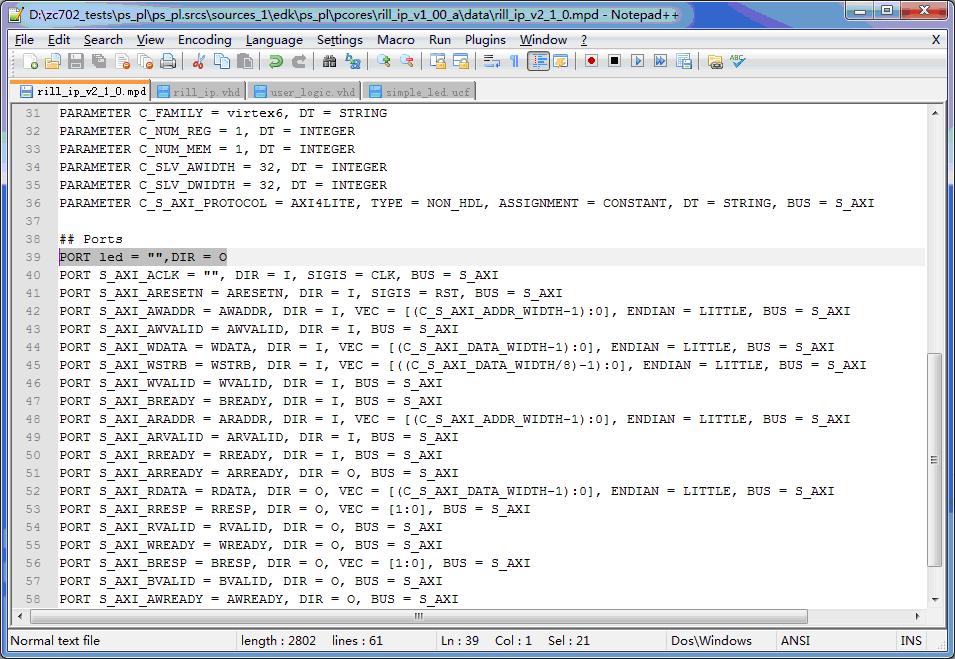

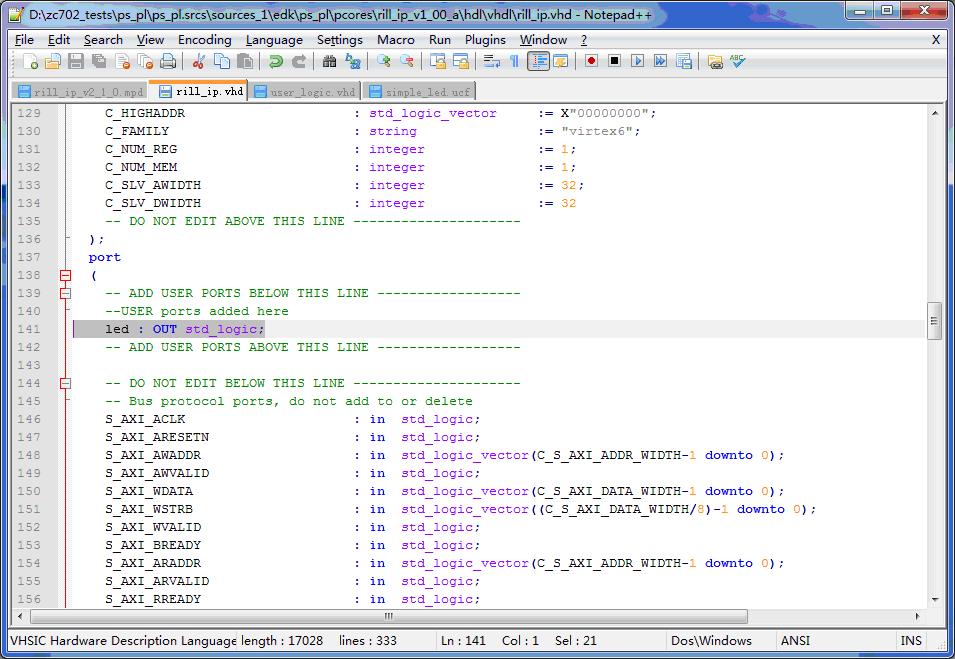

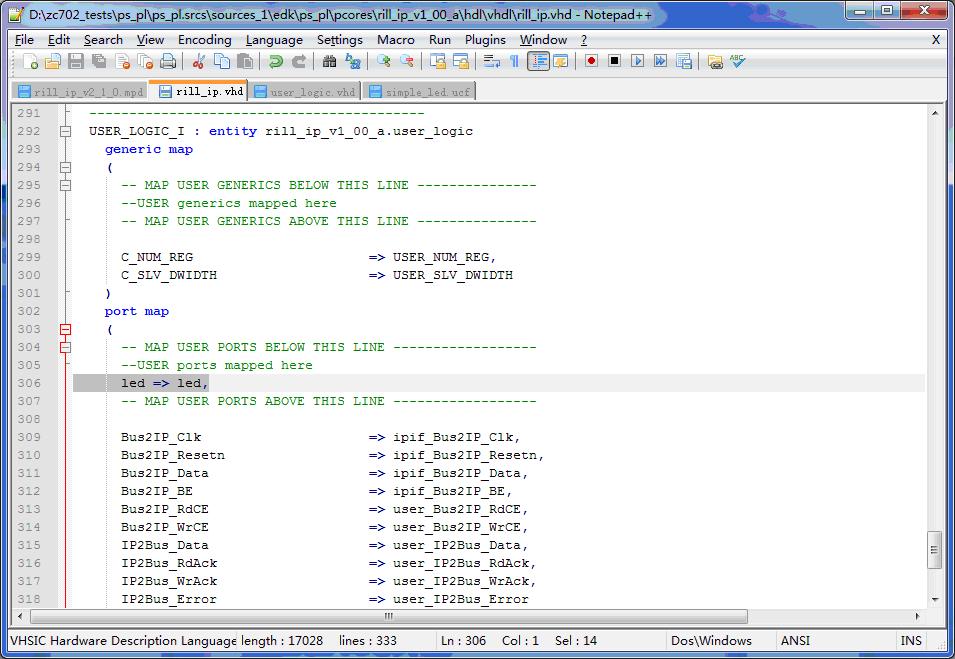

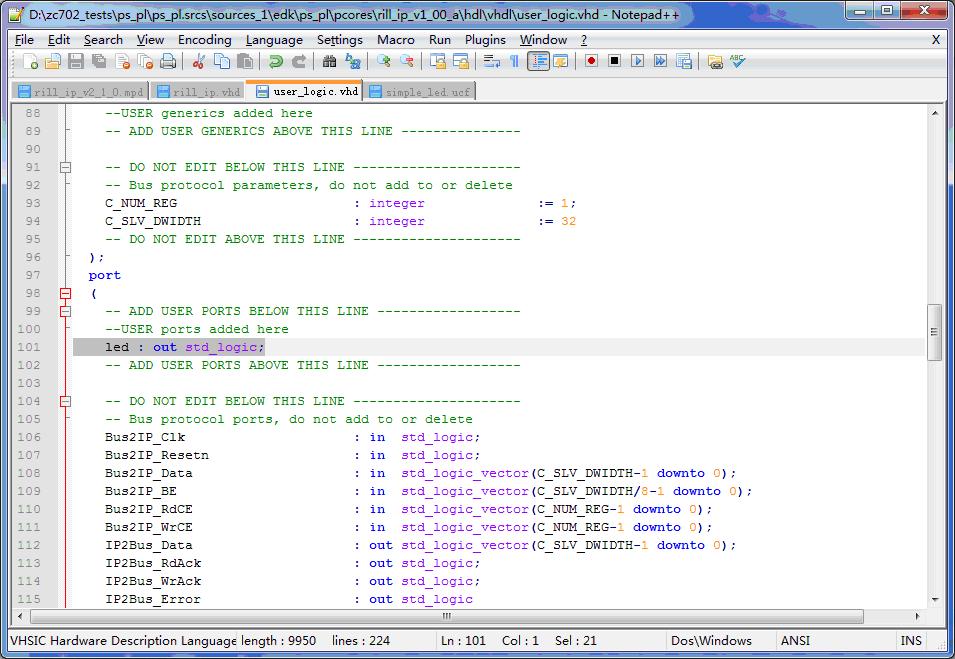

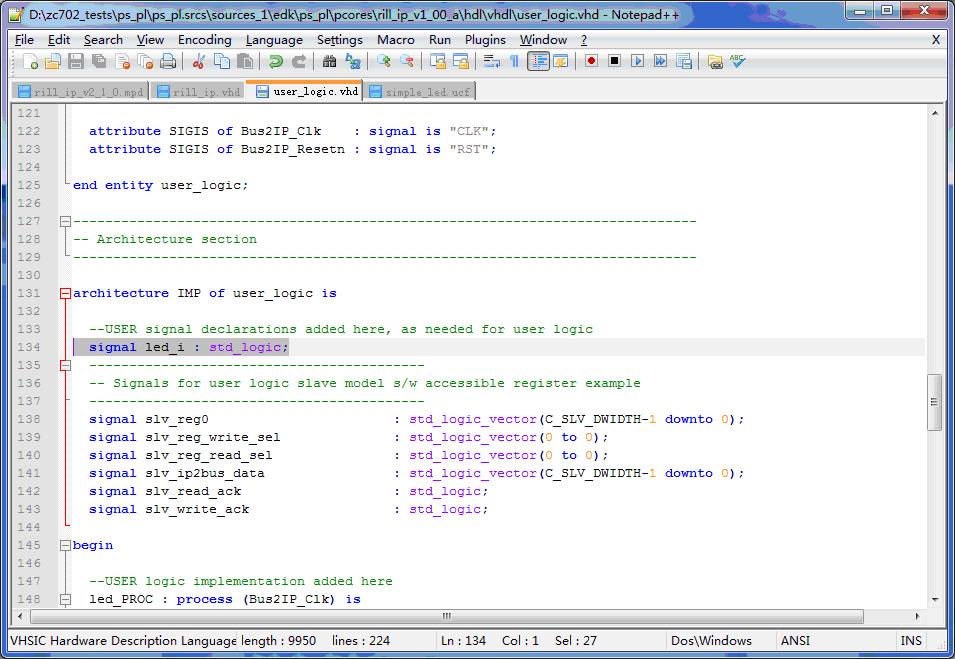

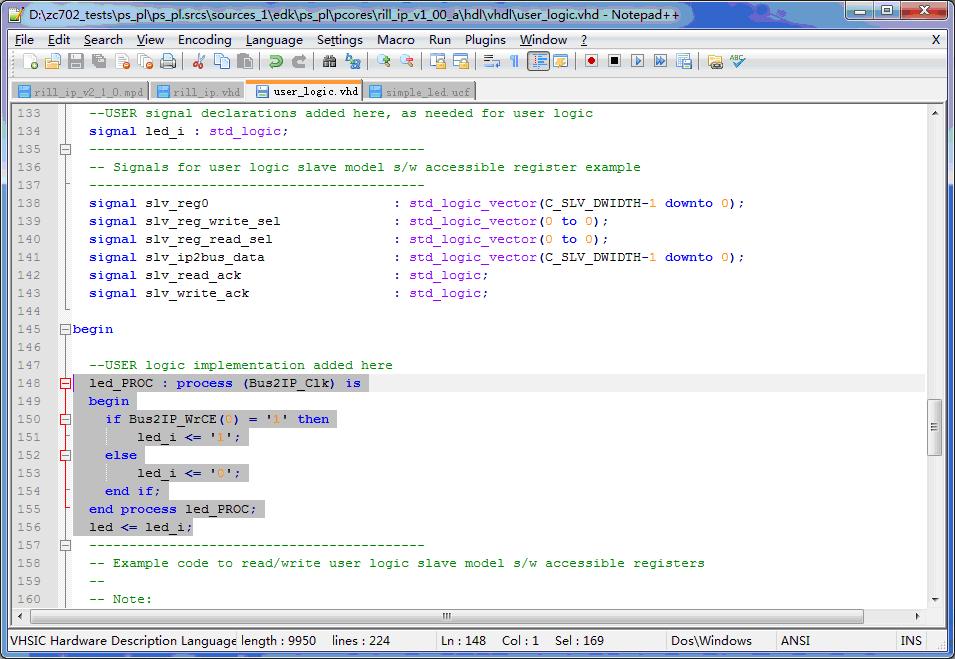

File:mpd,1个地方需要修改,如图:这3个文件的路径很深,不好找,截图上面有路径,方便很多。

可以根据截图找到对应位置,然后添加相应代码。

也可以参考附录代码。

File:rill_ip.vhd: 2个地方需要修改。

File:user_logic.vhd: 3个地方需要修改。

g) 将此ip添加到XPS工程。

h) 自动映射。注意port名称,ucf文件里要用。

i) 添加UCF文件,内容:ps_pl.ucf。

j) Create TOP HDL,然后生成bitstream。

k) 导出hardware,launch SDK。

l) 在SDK里创建helloword工程。

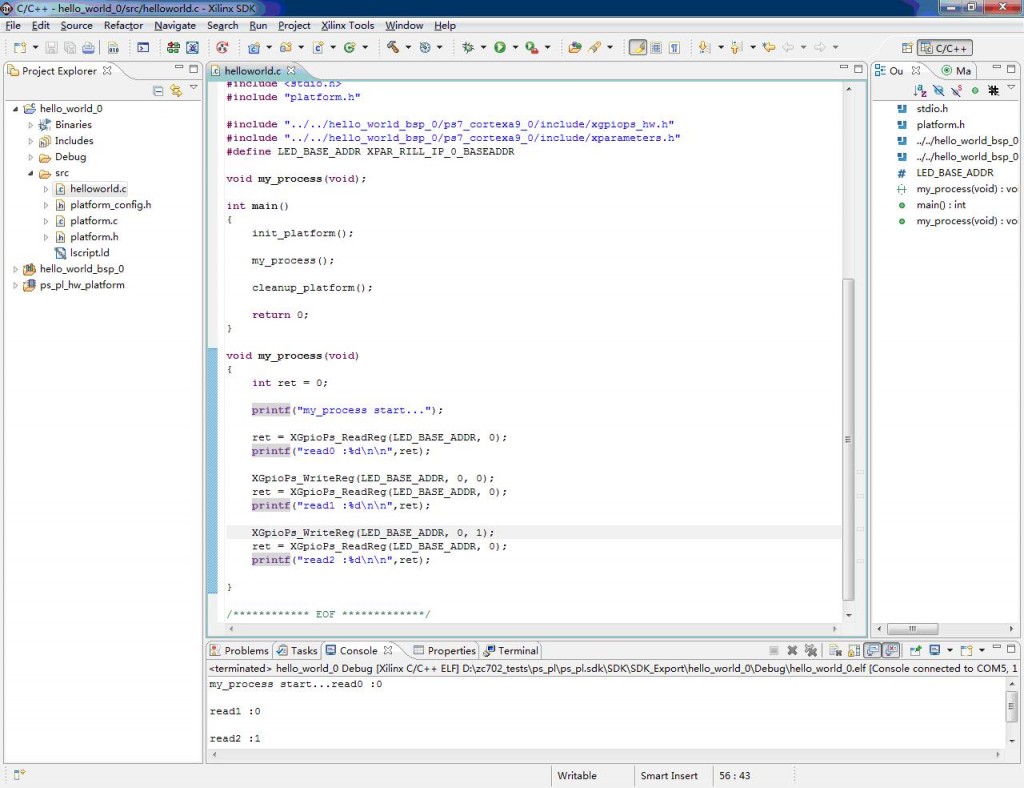

m) SDK编码,内容:helloworld.c。读写寄存器。

n) Program FPGA

o) Run AS,configure

p) Run

17.6 实验结果

看板子,DS18这个led会由亮变灭:串口也有打印。

,

附:

文件1:rill_ip_v2_1_0.mpd:

/* * Copyright (c) 2009 Xilinx, Inc. All rights reserved. * * Xilinx, Inc. * XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION "AS IS" AS A * COURTESY TO YOU. BY PROVIDING THIS DESIGN, CODE, OR INFORMATION AS * ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, APPLICATION OR * STANDARD, XILINX IS MAKING NO REPRESENTATION THAT THIS IMPLEMENTATION * IS FREE FROM ANY CLAIMS OF INFRINGEMENT, AND YOU ARE RESPONSIBLE * FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE FOR YOUR IMPLEMENTATION. * XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO * THE ADEQUACY OF THE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO * ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE * FROM CLAIMS OF INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY * AND FITNESS FOR A PARTICULAR PURPOSE. * *//* * helloworld.c: simple test application */#include <stdio.h>#include "platform.h"#include "../../hello_world_bsp_0/ps7_cortexa9_0/include/xgpiops_hw.h"#include "../../hello_world_bsp_0/ps7_cortexa9_0/include/xparameters.h"#define LED_BASE_ADDR XPAR_RILL_IP_0_BASEADDRvoid my_process(void);int main(){ init_platform(); my_process(); cleanup_platform(); return 0;}void my_process(void){int ret = 0;printf("my_process start...");ret = XGpioPs_ReadReg(LED_BASE_ADDR, 0);printf("read0 :%d\n\n",ret);XGpioPs_WriteReg(LED_BASE_ADDR, 0, 0);ret = XGpioPs_ReadReg(LED_BASE_ADDR, 0);printf("read1 :%d\n\n",ret);XGpioPs_WriteReg(LED_BASE_ADDR, 0, 1);ret = XGpioPs_ReadReg(LED_BASE_ADDR, 0);printf("read2 :%d\n\n",ret);}/************ EOF *************/总结

这三个实验包含了高端FPGA的主要的三种开发方式。也是典型的使用方式。这三个小实验搞明白了的话,就算入门了吧。

再进一步的话,只不过是逻辑复杂些,代码量多一些。这就需要其他方面的知识和技能了。